石墨烯基晶体管已被报道应用于高速器件,因其原子级厚度消除了基本迁移时间的限制。但是,目前已报道的石墨烯基区晶体管普遍采用隧穿发射结,然而隧穿发射结的势垒高度严重限制了该晶体管作为高速电子器件的发展前景。为了克服这个问题,这里提出了一种石墨烯基异质结晶体管,其中石墨烯夹在硅层之间。一种垂直结构的硅-石墨烯-锗晶体管被成功制备,通过单晶硅和单层石墨烯构造了肖特基发射结。所设计的肖特基发射结的电流达692 A cm-2,电容为41 nF cm-2,这使得器件总延迟时间缩短了1000倍以上,即器件的截止频率由约1.0MHz提升至1.2GHz。经过进一步的工程设计,该半导体-石墨烯-半导体晶体管为超高速运行器件的发展奠定了重要基础。

.png)

Figure 1.装置的设计与构造。(a)直接堆叠Si膜,单层石墨烯和Ge基底建造Si-Gr-Ge晶体管,(b)光学照片,(c)Si膜在石墨烯上的SEM图,(d)晶体管的横截面示意图。

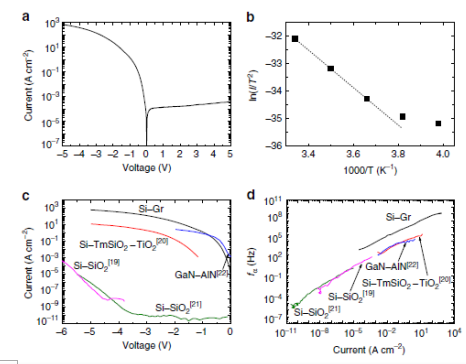

Figure 2. Si-Gr-Ge晶体管的肖特基发射结。(a)Si-Gr发射结在室温下的I-V曲线,(b)电流-温度相关曲线,(c)不同发射结情况下石墨烯基晶体管的电流比较,(d)不同发射结情况下石墨烯基晶体管的fa比较。

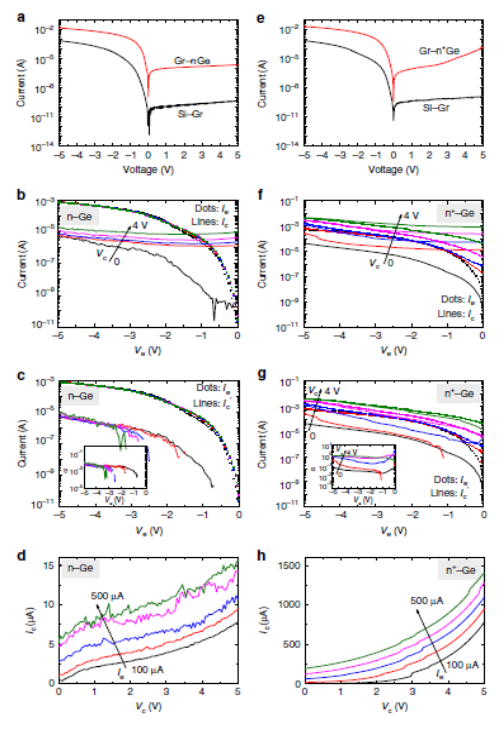

Figure 3. Si-Gr-Ge晶体管在常用基区模型下的电学特性表征。

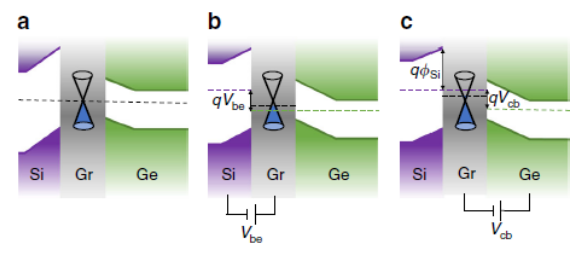

Figure 4. Si-Gr-Ge晶体管的能带图。(a)无施加偏压下的能带图,(b)给发射结施加一个大于零的正向偏压时的能带图,(c)给集流体结施加一个大于零的反向偏压时的能带图。

该研究工作由中国科学院金属研究所沈阳材料科学国家研究中心孙东明团队于2019年发表在Nature Communications国际顶级期刊上。原文:A vertical silicon-graphene-germanium transistor(https://doi.org/10.1038/s41467-019-12814-1)

|

|

| 您的称呼 : | |

| 联系电话 : | |

| 您的邮箱 : | |

| 咨询内容 : | |

|

|